Volume 119 No. 14 2018, 145-153

ISSN: 1314-3395 (on-line version)

## An Efficient FPGA Implementation of Fast Lifting Wavelet **Transform for Lossless Image Compression**

K.Ezhilarasan<sup>1</sup>, D.Jayadevappa<sup>2</sup>, Puspamala S<sup>3</sup>

<sup>1</sup>Research Scholar, Jain University, Sambhram IT, Bangalore, Karnataka <sup>2</sup>EIE Dept, JSSTEB, Karnataka <sup>3</sup>ECE, DSU, Bangalore, Karnataka \*Corresponding Email and Author: <sup>1</sup>murali981983@gmail.com \*2devappa.22@gmail.com \*3pushpasiddaraju@gmail.com

#### Abstract

This Paper proposes An efficient FPGA implementation of Fast Lifting Wavelet Transform (FLWT) for lossless image compression, The lifting based Discrete Wavelet Transform (LDWT) architecture has been selected for manipulating the correlation between the image pixels, here we provide the which storage element is required to store the computed wavelet coefficients and we will design the novel architecture to predict and update the pixel in lifting method using multiplier less operation, The use of this proposed structure allows implementation of symmetric extension without using additional computations, the proposed lifting based architectures gives a significant advantage over convolutional filter bank based architectures in terms of high throughput and less memory consumption. The proposed algorithm works a new memory structure which uses the dual line scanning and less number of registers for transposing unit, which leads to a low cost and simple hardware implementation. At lower bit rates, the PSNR is almost same to the original and modified versions and it is difficult to perceive the difference between the images coded by the different state of algorithms. But at higher bit rates, the PSNR is higher for the modified algorithm than the original one. The proposed implementation also uses multiplier-less operations for filter design at all the stages, using pipelining thereby ensuring a low power system and high-frequency operation and this will implemented in XC7Z020CLG484-1 with 100Mhz of frequency.

Keywords—: lossless compression, FPGA, row-column filtering,, DWT, medical images, 5/3 filter pair

#### 1. Introduction

The wavelet transform provides a time-frequency domain representation for the analysis of signals. Therefore, there are two main methods to produce and implement wavelet transforms. These methods are based on spatial domain and frequency domain features. The frequency-based method is Filter Banks (FB) and the time-based one is called Lifting Scheme. The Discrete Wavelet Transform (DWT) has become very popular signal processing tool over the past decades. It has been widely used effectively in signal and image processing application. Mallat[1] proposed the multiresolution represent of signals based decomposition. The advantage of DWT over other traditional transformations is that it performs multiresolution analysis of signals with localization both in time and frequency.

Today the DWT is being increasingly used for image compression, since it supports features like progressive image transmission (by quality, by resolution), ease of compressed image manipulation, a region of interest coding (ROI), etc. In fact, it is the basis of the new JPEG2000 image compression standard which has been shown to have superior performance compared to the current JPEG standard [2] DWT has traditionally been implemented by convolution or FIR filter bank structures. Such implementations require both a large number of arithmetic computations and large storage features that are not desirable for either high speed or low power image/video processing applications. Recently, a new mathematical formulation for wavelet transformation has been proposed by Swelden [3] based on the spatial construction of the wavelets and a very versatile scheme for its factorization has been suggested in [4]. This new approach is called the lifting-based wavelet transform or simply

lifting. The main feature of the lifting-based DWT scheme is to break up the high-pass and low-pass wavelet filters into a sequence of upper and lower triangular matrices, and convert the filter implementation into banded matrix multiplications [4]. This scheme often requires far fewer computations compared to the convolution-based DWT [3, 4].

Due to recent advances in the technology, implementation of the DWT on field programmable gate array (FPGA) and digital signal processing (DSP) chips has been widely developed. The lifting scheme the structural processing elements, including multipliers, are arranged serially; hence, the number of multipliers in each pipeline stage determines the clock speed of the structure. Based on [5], the main challenges in the hardware architectures for 1-D DWT are the processing speed and the number of multipliers, while for 2-D DWT it is the memory issue that dominates the hardware cost and the architectural complexity.

#### Lifting Wavelet Transform

The lifting procedure is gone for diminishing the number of change coefficients and developing the second era wavelets. Daubechies and Sweldons [4] and Sweldons [8] demonstrated that another structure of wavelet change can be built from any orthogonal and biorthogonal channels by utilizing factorization of a polyphase framework. So this plan, which is known as the lifting plan, starts with an outstanding arrangement of channels, say (h, g), and the channels are part of even and odd. The polyphase grid, given by

$$P(z) = \begin{bmatrix} h_{even}(z) & h_{odd}(z) \\ g_{even}(z) & g_{odd}(z) \end{bmatrix} \dots (1)$$

The polyphase matrix is factorized by using successive division approach and choosing appropriate Laurent's polynomial, it can be expressed as

$$P(z) = \prod_{i=1}^{m} \begin{bmatrix} 1 & S_i(z) \\ 0 & 1 \end{bmatrix} \begin{bmatrix} 1 & 0 \\ t_i(z) & 0 \end{bmatrix} \begin{bmatrix} K & 1 \\ 1 & 1/K \end{bmatrix} \dots (2)$$

Where K is a constant and the Laurent polynomial  $S_i(z)$  and  $t_i(z)$  are the prime and dual lifting stage respectively, here we chosen the filter bank as 5/3. This type of filter pair has the advantage of less area and high performance, it has smaller critical paths than the 9/7 filter pair. Consider this filter pair not only smaller number of lifting steps required but also it requires simple multiplications requires say 0.5 and 0.25 and this also implements using shift and add logic (SAL).the lifting scheme realize using four basic steps, they are Splitting, Prediction (P), Updating(U) and Scaling (K).

Fig. 1 General Structure of Lifting Wavelet Scheme

The prediction and update steps are for the most part iterated N times, with distinctive weights utilized at each cycle.

$$d_i^n = d_i^{n-1} + \sum_k P_n(k) S_k^{n-1}, n \in \{1, 2, 3, \dots, N\} \dots (3)$$

$$S_i^n = S_i^{n-1} + \sum_k U_n(k) d_k^n, n \in \{1, 2, 3, \dots, N\} \dots (4)$$

Where  $s_i^0$  and  $d_i^0$  are the even and odd components of input sequence for 5/3 filter pair with N=1, P<sub>1</sub>=-0.5 and U<sub>1</sub>=0.25, K=1, So, lifting scheme for 5/3 filter bank comprises of one prediction step and one update step that are calculated by following equations:

$$s_{i}^{0} = x_{2i} \text{ and } d_{i}^{0} = x_{2i+1}$$

$$d_{i}^{1} = d_{i}^{0} - \frac{1}{2} (s_{i}^{0} + s_{i+1}^{0}) \dots (5)$$

$$d_{i}^{1} = x_{2i+1} - \frac{1}{2} (x_{2i} + x_{2i+2}) \dots (6)$$

$$s_{i}^{1} = s_{i}^{0} + \frac{1}{4} (d_{i-1}^{1} + d_{i}^{1}) \dots (7)$$

$$d_{i-1}^{1} = x_{2i-1} - \frac{1}{2} (x_{2i-2} + x_{2i}) \dots (8)$$

### 3. Related Work

Lifting-based DWT has many benefits over convolution-based DWT as well as, quicker implementation, integer coefficients, absolutely in place calculation of DWT, less hardware complexity and symmetric forward and inverse transform. Different lifting wavelet architectures were described in [9,10,11]. Baruan et.al [6]

suggested that dual scan architecture with more hardware utilization and less computation time efficient architecture. Hence, memory size also reduced for intermediate stages, in additive with that it can be extended for multiwavelet using lifting transform and cascade the multidimensional DWT using basic 1D-DWT architectures. In conventional wavelet transform the irrational filter coefficients were used, to avoid that, the integer wavelet transform was proposed with addition and arithmetic shifting, which is close to original filter pair Zhang.et al [7] proposed efficient approach of 9-7 and 11-9 wavelet has different coefficients to reduce the hardware computation compared with conventional filter bank and implemented in FPGA. Jou et.al [12] proposed the first pipeline VLSI architecture for 1D biorthogonal filter bank using 9/7 filter. Andra et.al [12] presented the parallel block process based architecture for forward and reverse lifting operation for different default filters. Huang et.al [13] presented a systematic design method to develop the different efficient lifting wavelet based VLSI for 1D and 2D DWT through dependence graph formation and systolic array mapping. Hen et.al [18] proposed the direct and folded architecture for 5/3 filter and same implemented in VLSI.Haung et.al [15] presented the flipping structure to reduce the timing accumulation in conventional lifting based DWT architectures and also it reduces the critical path time and memory requirements. Liao et.al [14] proposed the recursive and dual scan architecture for 1D and 2D DWT. Huang et.al [19] presented the efficient single level 2D DWT architecture, in which the row element processor was designed by B-Spline to reduce the area while the column element processor was designed and it used for flipping and convolution approach. An et.al [16] proposed the 2D lifting DWT and IDWT, in that the multiplier operation was replaced by shift and add (SAA) operation and they proposed the general RAM based architecture to reduce the size of internal memory and control complexity and Lin [20] presented a modified lifting scheme by the arrangement of predict and update in a single step, this will minimize the critical path to one multiplier .Xiong et.al [21] proposed the high speed line based architecture for 2D lifting DWT with two row and column element processors to increase the through put as double the input and output. [4].Zhang et.al [22] presented a pipeline architecture for lifting 2D DWT to satisfy the need for high throughput requirements of real time applications. Oliver et.al [23] developed the architecture for line by line process technique to efficiently compute the 2D DWT with lower memory reducing the complexity. The memory Efficient pipeline 2D DWT architecture was developed by Lai et.al [24] with parallel scanning method, the architecture uses 2x2 register array with 4 times of N temporary memory. Mohanty and Mehar [25] developed a modular and pipeline lifting DWT architecture with that any line and frame buffer and thus architecture mainly scaled for high throughput as well as are constrained implementation. Hang et.al [26] presented the non- separable approach with control path for high speed and reduce area for 2D DWT lifting, here lifting 9/7 filter coefficients are floating point numbers, so multiplier are needed for hardware realization of DWT. The multiplier less wavelet filterbank for image compression proposed by [27, 28] to reduce the area and power.kotteri et.al [29] implemented the multiplier less 2D biorthogonal 9/7 filter and it was compared with convolutional based approach. Marbha.m and Masera.G [30] proposed the lifting 9/7 filter coefficients are truncated using canonical signed digit representation for multiplierless DWT and distributed arithmetic (DA) can be replace multipliers at the cost of memory and throughput. Acharyya et.al [31] proposed the convolution based 1D DWT architecture using DA to save the area and power. The lifting filter 5/3 coefficients are 0.5 and 0.25 are can be easily implemented with the arithmetic shift right operations was proposed by [32, 33] to achieve efficiency in area, power and throughput. The multipliers were replaced by SAA method, not like DA, thus does not use any memory for multiplier. Shi et.al [34] presented the efficient folded architecture with SAA method for lifting based DWT to reduce the area. Hsia et.al [35] proposed the memory efficient dual scan architecture with SAA to compute 2D lifting DWT with reduced latency with area overhead. Recently, Darji et al [35] proposed the efficient design and implementation of 2D DWT with lifting 9/7 filter bank and pipeline architecture for 2D DWT with a critical path of single adder. The proposed the method is to implement the efficient design of Fast lifting wavelet transform with dual scan memory and Z scanning method is use to reduce the latency and transposing the register array size constant coefficient multiplication operation are designed with the pipelined SAA to increase the speed and reduce the area and power.

## 4. Proposed Architecture

In this correlation, a single port image memory is considered. The image memory is normally off-chip. In any case, it might likewise be on-chip, on the off chance that we are managing little edges or potentially utilizing substantial FPGA devices. Considering the way that the image memory can now and again be on-chip, we made our correlation as bland as conceivable by utilizing a typical clock for the picture memory and whatever remains of the framework. Utilizing a single port image memory in our examination includes adaptability to the extent the accessible memory is worried, the same number of sheets do exclude multiport substantial memory squares. Additionally, since the image memory is ordinarily off-chip, the way that single port off-chip RAMs expend less vitality per access than multi-port ones is certainly an interesting point [37,38]. In information escalated calculations, for example, the 2D DWT, memory gets to are very incessant. Accordingly, when the picture memory is off-chip, from a vitality point of view single-port RAMs are perfect, exchanging off the higher execution of multi-port RAMs [38].

Generally, two memory units are utilized in image preparing frameworks: one to store the first image, and one for the yields. To stay away from the second unit, we utilized the set up mapping design: the channel's yields are composed over memory substance that are as of now devoured and never again required. To receive this design, every memory area ought to have a similar piece width as the yields of the change. The set up mapping plan is delineated. The dyadic descent is connected on a theoretical level 8x8 unique image and the yields of each stage are composed in memory areas that have as of now been perused and separated. The shaded regions, in Fig. 5, speak to the pixels of the coarse picture at the contribution of each level.

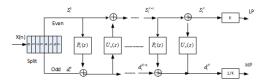

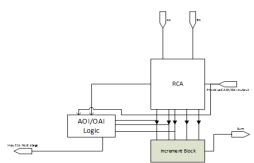

The Figure.2 shows that the hardware implementation of lifting wavelet transform in FPGA, and it has the memory unit, DWT 5/3 filter, control path based FSM model and on chip buffer. This consumes less memory in computation and less in critical path delay in the DWT filter. The on chip buffers are used for to store the coefficients of intermediate levels of filtering which increases the computation speed and reduces the memory consumption, it improves the memory access compared to the other scanning techniques.

Fig. 2 Implementation of lifting wavelet in FPGA

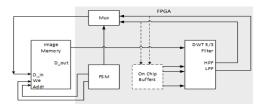

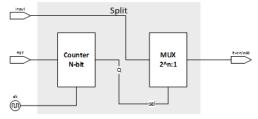

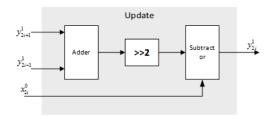

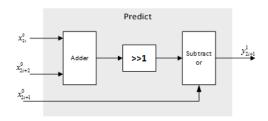

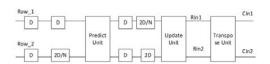

The figure 3. Shows that DWT 5/3 filter lifting wavelet scheme, consists of three operations will be performed, they are splitting, prediction and updating, when the input image pixels are applied in to the splitting steps, it splits the odd and even samples and it fed in to the prediction unit. The prediction units has 2 adders/subtractor and 1 arithmetic shift registers. After computation of prediction, the result will be fed in to the update unit, it has 2 adder and 1 arithmetic shift registers which produces the low pass filter coefficients and high pass coefficients.

Fig. 3 DWT 5/3 Lifting Wavelet Scheme

The proposed architecture 2D-DWT 5/3 lifting scheme shown in figure 3. Each DWT produces four subbands i.e, LL, LH, HL and HH which are connected to the temporary processor to perform transform output of these temporary transform consists of a low frequency coefficients and high frequency coefficients. The figure 4.(a),(b) and (c) shows that the internal architecture of splitting, Predict and Update Unit. The single filter is used in vertical filtering and horizontal filtering. The choice of using the row column architecture is mainly it uses single port read only memory.it is simple to design and it reduces the hardware cost and critical path time delay and also less number of lifting steps required compare to other filter techniques. It's symmetric and orthonormal.

Fig. 4(a) Internal Architecture for Split Unit

Fig. 4(b) internal architecture of Update Unit

Fig. 4(c) Internal Architecture of Predict Unit

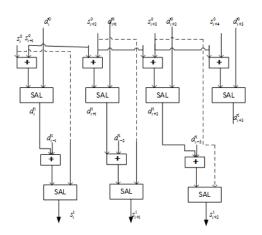

The figure 5 shows the data signal flow graph of the processing element unit and internal architectures of processing element of Row processing and Column processing element. The proposed scheme has been designed with pipelining processing unit, The operation of 1D DWT as follows, the input image pixel is split in to even and odd samples which is known as lazy wavelet, then the odd samples receive the predicted module during first clock cycle, then the even input sample and previous even input sample are added, then the previous odd sample is multiplied with the first filter coefficients during the second and third clock cycles, during this time shift and add arithmetic operation were performed. During fourth clock cycle the shift and add result is added with the odd sample input which gives the result of predict output. During fifth clock cycle the present predict value and the previous predict value along with the past even input sample gives the updated value. The signal flow graph shows that only adders are required to compute the each of clock cycle, so that the critical path can be limited with the delay.

Fig. 5 Data flow graph of 5/3 lifting scheme

In this section we propose the new efficient high speed memory lifting based 2D DWT architecture. This processor consists of row processor (RP) and column processor (CP) and with this we will add the pipeline and share the computational load with in the pipeline stages The proposed scheme uses the line based scanning method to trade-off between internal and external memory. Pipelining lift 5/3 1D-DWT processor has been performed by using the processing unit (PU) in the proposed scheme shown in Figure 6. The proposed architecture reduces the number of registers in the transposing unit and control the critical path delay in conventional carry skip adder (CCSA).

Fig. 6(a) detailed Architecture of 5/3 Filter

To calculate high speed computation, pipelining is required to reduce the critical path. Since the multiplication dominates the execution of most DSP algorithm, so there is necessity of high speed multiplier. A serial multiplier gives less area and power with high processing delay. In array based multiplier partial product are used for sequential addition, it while reduce the speed of the operation. The conventional carry skip adder (CCSA) based multiplier have lower area but it uses more number of transistors and consume huge processor. Compared to other multiplier, shift and adder arithmetic been widely used in many application become it yield smaller area requirement and also gives efficient pipelining to reduce the critical path which gives high speed.

Fig. 6(b) Modified Conventional CSA

Fig. 7(a) Hardware structure of Row Processing Unit

The figure 6.(b) shows that the modified conventional carry skip adder (CCSA) gives the fast carry skips by utilizing the AOI and OAI logic in place of mux. The impact of dimension sizing provides efficient skips have a processing a fusion model of skip adder scheme relying upon the expansion about mentioned skip adder with replacement of few intermediate blocks. The A and B two inputs variables fed in to each stage of the CCSA and there are it has n-stages. Each phase consist of Ripple Carry Adder (RCA) along with the extend having AOI and OAI. The sum of RCA is fed in to the increment block that produces the final sum. The increment block consists of half adders to reduce the chain delay and AOI and OAI are very important in CMOS logic behaviously they can perform two levels of logic but implemented in just single level of transistors.

#### 4.1 Row and Column Processing Element

Fig. 7(b) Hardware structure of Column Processing Unit

The dataflow for vertical filtering is similar to horizontal filtering, the only difference is that the vertical filtering is given as input to from the line buffer in the place of image data. However, instead of computing the whole sub band in a shot, we need to compute next eight data as soon as enough data are available. Therefore, we need to compute directly on eight pixel using DWT by one pass without Reloading the samples from images. In order to reduce the memory usage and avoiding clash of storage intermediate results, a compression is required. We kept the original lifting scheme by factor substitution. Instead of update the new value in the temporary buffer every time, we need to compute the low pass and high pass output first and then calculate the temporary result for next stage. Now we split the line buffer in to two categories, they are signal memory and temporary memory. The signal memory stores both the low pass and high pass samples from the 1D-DWT module 3 lines of signal memory are required to store the horizontal filtering output or row processing element and 3 lines are of temporary memory is required for intermediate results of vertical filtering. Every stage has 2 lines of signal will be consumed in signal memory and 1 line for next eight samples are generated and 3 lines of temporary results are transmitted in to temporary memory. In order to develop the different levels of decomposition, we should buffer 3 lines for every eight samples because only (LL)<sup>n</sup> outputs are required. In the DWT decomposition for next eight sample the length of the line buffer is exponentially decreased by 2 per eight. Assume there are J rows, each row has eight samples and the length of the image is NxN. The corresponding memory usage can be expressed as Signal Memory (S<sub>M</sub>) and Temporary Memory<sup>TM</sup>

$$S_{M} = 3 * \left[ N \left( 1 + 1/2 + 1/4 + \dots + 1 \setminus 2^{j-1} \right) \right]$$

$$= 6N \left[ 1 - \left( 1/2 \right) \right]^{J} \dots (10)$$

$$T_{M} = 3 * \left[ N/2 \left( 1 + 1/2 + 1/4 + \dots + 1 \setminus 2^{j-1} \right) \right]$$

$$= 3N \left[ 1 - \left( 1/2 \right) \right]^{J} \dots (11)$$

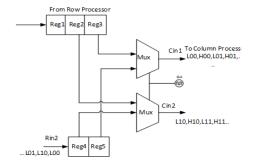

Fig. 7(c) Hardware Structure of transpose and Re-transpose Unit

The predict and update module lifting steps are fully pipelined to improve the computational speed. Predict and update module of lifting stage in Row processing unit, Column Processing unit shown in figure 7.(a) and (b) the lifting stage proposed architecture used total four adder/subtractor and two arithmetic logic shifter. The two stage pipelined architecture of 1D row and column processing element shown in figure 8 respectively. Where each predict and update module stage are pipelined through pipelined register and specified as 'D'.Two delay registers to hold the even input sample and three pipelined register for predict unit, totally five delay registers are required at the input of row

processor as shown in figure 2D/N register. In the In case of column process unit, three delay registers are required at the input of predict unit shown in figure. The output of predict row/column stage delayed by total six clock cycles to compensate three and two clocks delay in pipelined stage of predict unit and update unit respectively one delay for 2D/N shift register of row processor and column processor.

In the proposed Method, the RP expends two-input Pixels and produces two 1D DWT coefficients for every clock In the proposed design, the RP expends two-input pixels and produces two 1D DWT coefficients for every clock cycle. Yield of RP is given to TU, which transposes the approaching coefficients and gives contributions to the CP. The cycle. Yield of RP is given to TU, which transposes the approaching coefficients and gives contributions to the CP. The CP is likewise intended to give throughput of 2-input/2-yield per clock cycle. Generally, the line examine based 2D DWT plans requires transposing support of 1.5N size, while the proposed conspire needs just five registers in view of plans requires transposing cushion of 1.5N size, while the proposed conspire needs just five registers as a result of appropriation of Z-scan technique. Four temporary memory cushions with measure N are required in CP to hold past predict and update values.

The output request of the RP and info request of the CP is appeared by Figur.7 (a). The TU has a changing system to support two interchange 1D push coefficients to CP to perform finish 2D DWT. A proficient TU is presented here, which uses just five registers with two 2 × 1 multiplexers as appeared in Figur.7(c). The proposed TU is region and power proficient and autonomous of image estimate on the grounds that the Z-scan encourage two 1D DWT push coefficients of progressive lines in the progressive clock cycles to begin segment preparing when contrasted with TU proposed by line-based designs [15, 20] where, the CP needs to sit tight for whole column. The information stream of the proposed transposing unit is appeared in Table 1 and Table II gives the processor assignment and schedule of hardware structure.

Table I Processor Assignment and Schedule of 5/3 Filter Implementation

| Clock | Row Processor |              |              | Column Processor |              |       |

|-------|---------------|--------------|--------------|------------------|--------------|-------|

|       | Add-1         | Shift<br>Reg | Add-2        | Add-1            | Shift<br>Reg | Add-2 |

| 0     | -             | -            | -            | -                | -            | -     |

| 1     | X0+X2         | -            | -            | -                | -            | -     |

| 2     | X2+X4         | Reg1         | -            | -                | -            | -     |

| 3     | X4+X6         | Reg1         | Rs-<br>X1=Y1 | -                | -            | -     |

| 4     | X6+X8         | Reg1         | Rs-<br>X3=Y3 | -                | -            | -     |

| 5     |               | Reg1         | Rs-<br>X5=Y5 | Y1+Y3            | -            | Y0    |

| 6     |               | -            | Rs-<br>X7=Y7 | Y3+Y5            | Reg1         | Y0    |

| 7     |               |              |              | Y5+Y7            | Reg1         | Rs+X2 |

| 8     |               |              |              |                  | Reg1         | Rs+X4 |

| 9     |               |              |              |                  |              | Rs+X  |

Table II Data Flow of Transpose Unit of 5/3 filter

| Cloc | Rin      | Rin      | Reg      | Reg      | Reg      | Reg      | Reg      | Cin      | Cin             |

|------|----------|----------|----------|----------|----------|----------|----------|----------|-----------------|

| k    | 1        | 2        | 1        | 2        | 3        | 4        | 5        | 1        | 2               |

| 0    | $H_{00}$ | $L_{00}$ | -        | -        | -        | -        | -        | -        | -               |

| 1    | $H_{10}$ | $L_{10}$ | $H_{00}$ | -        | -        | $L_{00}$ | -        | -        | -               |

| 2    | $H_{01}$ | $L_{01}$ | $H_{10}$ | $H_{00}$ | 1        | $L_{10}$ | $L_{00}$ | $L_{10}$ | L <sub>00</sub> |

| 3    | $H_{11}$ | $L_{11}$ | $H_{01}$ | $H_{10}$ | $H_{00}$ | $L_{01}$ | $L_{10}$ | $H_{10}$ | H <sub>00</sub> |

| 4    | $H_{02}$ | $L_{02}$ | $H_{11}$ | $H_{01}$ | $H_{10}$ | $L_{11}$ | $L_{01}$ | $L_{11}$ | $L_{01}$        |

# 5. Implementation Results and Performance Comparison

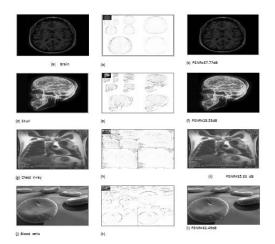

First, the peak to signal noise ratio (PSNR) is calculated for the different medical images for qualitative analysis. For qualitative analysis is performed on medical images size of 256x256. The test images are brain, blood cells, chest, and skull, shown in figure 9(a-l) here we applied three levels of decomposition and we observed that the least PSNR is 28.53dB and loss in the value of PSNR is not significant to human eye perception. The original image brain has most PSNR 37.77 compared to other original images followed by chest-Xray image. The figure shows the original image and the decomposition levels and the processed image.

The pipelining implementation of 1D lifting DWT processing element using multiplier with Z scanning shown in figure 8. The architecture proposed is extended to 2d-DWT and synthesized using Field Programmable Gate Array (FPGA) target. He we used the Xilinx Vivado 2016.2 and the device is XC7Z0CLG484-1. The FPGA performance comparison of proposed method shown in Table III. The proposed design is high speed as compared to design proposed by [39] and [40] because of small modification with almost same hardware utilization. The maximum Frequency it will be run for 100MHZ in this device compare to the existing methods it has efficient it has number of LUTs, Flip flops, LUTRAM,IO and BUFG, on Chip Memory, Power Dissipation and delays. The existing technique [40] has 35MHZ in the XC4VLX25 device which has less throughput with more latency.

Fig. 9 (a-d-g-j) Original image, (b-e-h-k) Decomposition level=3, Compressed Image (c,f,I,l)

The Proposed architecture which run for Maximum of 100Mhz with less latency. The Table III shows that the device utilization summary comparison with the existing Technique for different devices.

**Table III Device Utilization Summary**

|               | Existing method [39] | Proposed Method |

|---------------|----------------------|-----------------|

| Target device | XC4VLX25             | XC7Z020CLG484   |

| frequency     | 35MHz                | 100MHz          |

| LUTs          | 13356/21504          | 1252/53200      |

| Flip Flops    | 1439/21504           | 971/106400      |

| IOB           | 79/242               | 22/200          |

| GCLKs         | 1/32                 | 1/32            |

The LUT is occupied more in existing technique compared to the proposed method due to usage of hardware is very less and Flip Flop also is very less compared to existing technique run for high frequency

**Table IV Timing Consideration**

| Worst Negative Slack(WNS)  | 0.385ns     |

|----------------------------|-------------|

| Total Negative Slack (TNS) | 0 ns        |

| Worst Hold Slack (WHS)     | 0.086 ns    |

| Pulse Width Slack (WPWS)   | 3.75 ns     |

| Total on-Chip Power        | 0.135 Watts |

| Critical Path Delay        | 0.710 ns    |

| Data Path Delay            | 9.350 ns    |

| Logic Delay                | 2.454 ns    |

| Net Delay                  | 6.896 ns    |

| Clock Skew                 | 0.018 ns    |

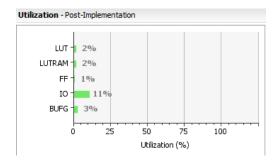

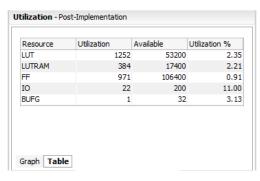

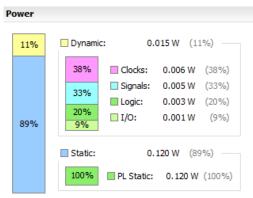

With the Timing constraints, the total Negative slack is 0.385ns and the total on chip poer is 0.135 w, which has the dynamic power utilization is 0.015w and static power utilization is 0.120w and after post implementation utilization summary has shown in the figure 10.(a) and (b).

| Total On-Chip Power:                | 0.135 W         |  |  |

|-------------------------------------|-----------------|--|--|

| Junction Temperature:               | 26.6 °C         |  |  |

| Thermal Margin:                     | 58.4 °C (4.9 W) |  |  |

| Effective &JA:                      | 11.5 °C/W       |  |  |

| Power supplied to off-chip devices: | 0 W             |  |  |

| Confidence level:                   | <u>Medium</u>   |  |  |

<u>Implemented Power Report</u>

Fig. 10(a) Utilization of hardware - Post Implementation

Fig. 10(b) Utilization of Hardware components in device

Fig. 10c Power Utilization in the device

#### Conclusion 6.

The fast efficient lifting DWT 5/3 wavelet transform computation has been designed with the multiplierless operation and Z scanning for computation of intermediate values, and less hardware utilization for Transposing Unit registers to reduce the hardware complexity, and also we used to modified conventional carry skip adder to perform the computation fast enough and we used the Xilinx Vivado 2016.2 with the target device as XC7Z020CLG484-1 which runs at 100Mhz and the critical path also reduced. The DWT 5/3 filter is very simple to implement compared to other filter bank. The power utilization of dynamic and static power dissipation is less and Total on chip power is 0.135 watts compared to the existing techniques, the feature work can be carried out for higher frequency with different filters with less hardware complexity.

#### References

- [1] S. Mallat, "A Theory for Multiresolution Signal Decomposition: The Wavelet Representation," IEEE Trans. Pattern Analysis And

- Machine Intelligence, vol. 11, no. 7, 1989, pp. 674–693.

T. Acharya and P. S. Tsai, JPEG2000 Standard for Image Compression: Concepts, Algorithms, and VLSI Architectures. John

- Wiley & Sons, Hoboken, New Jersey, 2004

W. Sweldens, "The Lifting Scheme: A Custom-Design

Construction of Biorthogonal Wavelets," Applied and Computational Harmonic Analysis, vol. 3, no. 15, 1996, pp. 186-

- Daubechies and W. Sweldens, "Factoring Wavelet Transform into Lifting Schemes," The J. of Fourier Analysis and Applications, vol. 4, 1998, pp. 247–269.

- C.-T. Huang, P.-C. Tseng, L.-G. Chen, Flipping structure: an efficient VLSI architecture for lifting-based discrete wavelet transform, IEEE Trans. Signal Process. 52 (2004), pp. 1080-1089.

- Barua, S., Carletta, J. E. E., Kotteri, K. a. A., & Bell, a. E. E. (2005). An efficient architecture for lifting-based two-dimensional discrete wavelet transforms. Integration, the VLSI Journal, 38(3),

- 341–352. http://doi.org/10.1016/j.vlsi.2004.07.010

Zhang, Z. (2003). Popular biorthogonal wavelet filters via a lifting scheme and its applications in image compression. IEE Proc Signal Process.., 150(4), Vis.Image http://doi.org/10.1049/ip-vis

- W. Sweldens, "The lifting scheme: A construction of secondgeneration wavelets," SIAM J. Math. Anal., vol. 29, no. 2, pp. 511-

- Lian, C.J., Chen, K.F., Chen, H.H., Chen, L.G.: 'Lifting based discrete wavelet transform architecture for JPEG 2000'. Proc. IEEE Int. Symp. on Circuits Syst., 2001, vol. 2, pp. 445-445

- Shiau, Y.H., Jou, J.M., Liu, C.C.: 'E cient architectures for the biorthogonal wavelet transform by filter bank and lifting scheme', IEICE Trans. Inf. Syst., 2004, E87-D2569, pp. 1867-1877

- [10] Tseng, P.C., Huang, C.T., Chen, L.G.: 'Generic RAM-based architecture for two-dimensional discrete wavelet transform with line-based method', IEEE Trans. Circuits Syst. Video Technol., 2005, 15, (7), pp. 910–920 IET.

- [11] Andra, K., Chakrabati, C., Acharya, T.: 'A VLSI architecture for lifting-based forward and inverse wavelet transform', IEEE Trans.

- Signal Process., 2002, 50, (4), pp. 966–977.

[12] Huang, C.T., Tseng, P.C., Chen, L.G.: 'Efficient VLSI architectures of lifting-based discrete wavelet transform by systematic design method'. Proc. IEEE Int. Symp. on Circuits Syst., 2002, vol. 2, pp. 565-568

- [13] Liao, H., Mandal, M.K., Cockburn, B.F.: 'Efficient architectures for 1-D and 2-D lifting-based wavelet transforms', IEEE Trans. Signal

- Process., 2004, 52, (5), pp. 1315–1326

[14] Haung, C.T., Tseng, P.C., Chen, L.G.: 'Flipping structure: an efficient VLSI architecture for lifting-based discrete wavelet transform', IEEE Trans. Signal Process., 2004, 52, (4), pp. 1080-1089.

- [15] Lan, X., Zheng, N., Liu, Y.: 'Low-power and high-speed VLSI architecture for lifting-based forward and inverse wavelet transform', IEEE Trans. Consum. Electron., 2005, 51, (2), pp. 379– 385.

- [16] Tseng, P.C., Huang, C.T., Chen, L.G.: 'Generic RAM-based architecture for two-dimensional discrete wavelet transform with line-based method', IEEE Trans. Circuits Syst. Video Technol., 2005, 15, (7), pp. 910-920.

- Chen, P.-Y.: 'VLSI implementation for one-dimensional multilevel lifting-based wavelet transform', IEEE Trans. Comput., 2004, 53, pp. 386-398.

- [18] Huang, C.T., Tseng, P.C., Chen, L.G.: 'Analysis and VLSI architecture for 1-D and 2-D discrete wavelet transform', IEEE Trans. Signal Process., 2005, 53, pp. 1575–1586.

- [19] Wu, B., Lin, C.: 'A high performance and memory efficient pipeline architecture for 5/3 and 9/7 discrete wavelet transform of JPEG 2000 Codec', IEEE Trans. Circuits Syst. Video Technol., 2005, 15, (12), pp. 1615-1628.

- , Tian, J., Liu, J.: 'Efficient high speed/low power line based architectures for two-dimensional discrete wavelet transform using lifting scheme', IEEE Trans. Circuits Syst. Video Technol., 2006, 16, pp.

- [21] Zhang, C., Long, Y., Kurdahi, F.: 'A hierarchical pipelining architecture and FPGA implementation for lifting-based 2-D DWT', J. Real-Time Image Process., 2007, 2, (4), pp. 281–291

- Oliver, J.-., Malumbres, M.-P.: 'Analysis and VLSI architecture for 1-D and 2-D discrete wavelet transform', IEEE Trans. Circuits Syst. Video Technol., 2008, 18, (2), pp. 237–248

- Lai, Y.-K., Chen, L.-F., Shih, Y.-C.: 'A high-performance and memory-efficient VLSI architecture with parallel scanning method for 2-D lifting-based discrete wavelet transform', IEEE Trans.

- Consum. Electron., 2009, 55, (2), pp. 400–407.

[24] Mohanty, B.K., Meher, P.K.: 'Memory efficient modular VLSI architecture for high-throughput and low-latency implementation of multilevel lifting 2-D DWT', IEEE Trans. Signal Process., 2011, 59, (4), pp. 2072–2084

- Zhang, W., Jiang, Z., Gao, Z., Liu, Y.: 'An efficient VLSI architecture for lifting-based discrete wavelet transform', IEEE Trans. Circuits Syst. II, 2012, 59, (3), pp. 158-162.

- [26] Kotteri, K., Bell, A., Carletta, J.: 'Design of multiplierless, high-performance, wavelet filter banks with image compression applications', IEEE Trans. Circuits Syst. I: Regul. Pap., 2004, 51, (3), pp. 483-494.

- Martina, M., Masera, G.: 'Multiplierless, Folded 9/7-5/3Wavelet VLSI Architecture', IEEE Trans. Circuits Syst. II: Express Briefs, 2007, 54, (9), pp. 770-774.

- [28] Kotteri, K., Barua, S., Bell, A., Carletta, J.: 'A comparison of hardware implementations of the biorthogonal 9/7 DWT: convolution versus lifting', IEEE Trans. Circuits Syst. II: Express Briefs, 2005, 52, (5), pp. 256–260.

Martina, M., Masera, G.: 'Low-complexity, efficient 9/7 wavelet

- filters VLSI implementation', IEEE Trans. Circuits Syst. II: Express Briefs, 2006, 53, (11), pp. 1289-1293.

- [30] Acharyya, A., Maharatna, K., Al-Hashimi, B., Gunn, S.: 'Memory reduction methodology for distributed-arithmetic-based methodology distributed-arithmetic-based DWT/IDWT exploiting data symmetry', IEEE Trans. Circuits Syst. II: Express Briefs, 2009, 56, (4), pp. 285–289.

[31] Darji, A., Bansal, R., Merchant, S., Chandorkar, A.: 'High speed

- VLSI architecture for 2-D lifting DiscreteWavelet Transform'.

- Proc. Int. Conf. on Design and Architectures for Signal and Image Processing (DASIP), 2011.

- [32] Darji, A., Merchant, S., Chandorkar, A.: 'Efficient pipelined VLSI architectre with dual scanning method for 2-D lifting-based discrete wavelet transform'. Proc. Int. Symp. Integrated Circuits (ISIC), 2011, pp. 329–331.

- [33] Shi, G., Liu, W., Zhang, L., Li, F.: 'An efficient folded architecture for lifting-based discrete wavelet transform', IEEE Trans. Circuits Syst. II, 2009, 56, (4), pp. 290–294

- [34] Hsia, C.-H., Chiang, J.-S., Guo, J.-M.: 'Memory-efficient hardware architecture of 2-D dual-mode lifting-based discrete wavelet transform', IEEE Trans. Circuits Syst. Video Technol., 2013, 23, (4), pp. 671–683.

- [35] Darji, A., Arun, R., Merchant, S. N., & Chandorkar, 'A Multiplier-less pipeline architecture for lifting-based two-dimensional discrete wavelet transform. *IET Computers & Digital Techniques*, 2015, 113–123. http://doi.org/10.1049/iet-cdt.2013.0167.

- Wavetet unstollin. The Computer's & Digital Techniques, 2015,

113–123. http://doi.org/10.1049/iet-cdt.2013.0167.

[36] N. D. Zervas, G. P. Anagnostopoulos, V. Spiliotopoulos, Y. Andreopoulos, and C. E. Goutis, "Evaluation of design alternatives for the 2-D-discrete wavelet transform," IEEE Transactions on Circuits and Systems for Video Technology, vol. 11, no. 12, 2001, pp. 1246–1262

- pp. 1246–1262

[37] C.-T. Huang, P.-C. Tseng, and L.-G. Chen, "Analysis and VLSI Architecture for 1-D and 2-D Discrete Wavelet Transform," IEEE Transactions on Signal Processing, vol. 53, no. 4, 2005, pp. 1575–1586

- [38] J. Jyotheswar and S. Mahapatra, "Efficient FPGA implementation of DWT and modified SPIHT for lossless image compression," J. Syst. Archit., vol. 53, no. 7, pp. 369–378, 2007.

- Syst. Archit., vol. 53, no. 7, pp. 369–378, 2007.

[39] M. E. Angelopoulou, K. Masselos, P. Y. K. Cheung, and Y. Andreopoulos, "Implementation and comparison of the 5/3 lifting 2D discrete wavelet transform computation schedules on FPGAs," J. Signal Process. Syst., vol. 51, no. 1, pp. 3–21, 2008.